转发一篇好文章

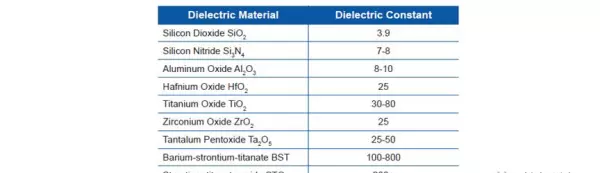

K指的是介电常数,衡量材料储存电荷能力。按介电常数的高低分为低介电(low-k)材料和高介电(high-k)材料。一般Low-K材料介电常数低于3.0;high-k材料是相对于SiO2而言,只要介电常数大于SiO2的介电常数3.9,一般都称为High-K材料。

为什么要采用High-K材料?

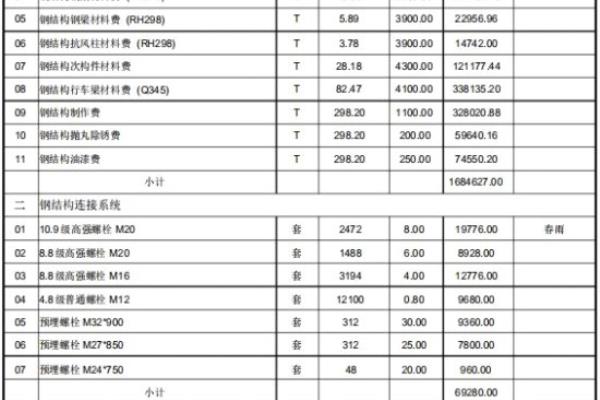

随着工艺尺寸的减小,栅极介质厚度不断减薄,电子直接隧穿引起的栅极漏电流随之增大。如何平衡漏电流的增大和工艺尺寸减薄之间的矛盾呢?high-k的使用发挥了重要作用。这里需要提出EOT等效氧化层厚度的概念。

除了高的k值,在半导体工艺中,还需要考虑材料势垒、能隙、界面态密度和缺陷、材料的化学和热稳定性,与标准CMOS工艺的兼容性等因素。HfO2族是目前high-k材料的主要选择。

但high k介质和多晶硅栅极之间会形成键合,产生“费米钉轧现象”,即无法通过多晶硅掺杂调节阈值电压;另外器件的电子迁移率也因偶极性分子振动降低,因此高k介质和多晶硅栅的兼容性不是很好。而金属栅极的使用可以解决相容性问题,这就是我们后来常常听到的HKMG工艺。

为什么采用Low-K材料?

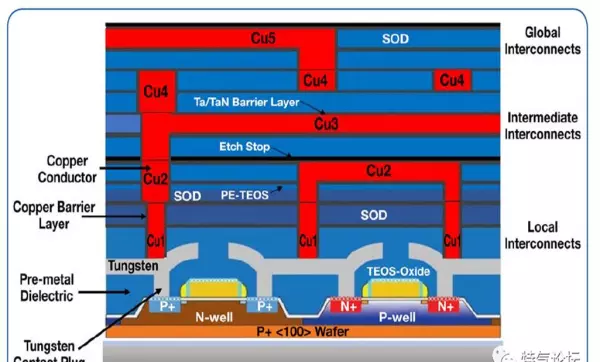

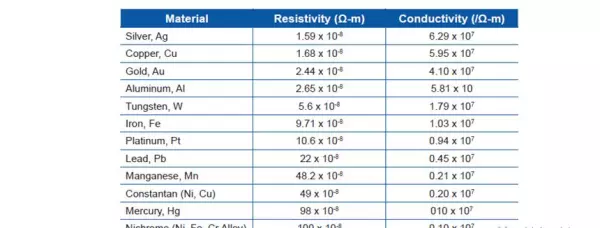

集成电路密集度提高,导体连线数目也在增加,由金属连接线造成的电阻电容延迟现象, 不仅影响芯片的速度,也对工作可靠性构成严重威胁。电路信号传输速度取决于寄生电阻与寄生电容二者乘积。要解决RC delay的问题,就需要降低寄生电阻和寄生电容。寄生电容正比于电路层隔绝介质的介电常数k,因而使用低k材料作为不同电路层的隔绝介质,即可达到减小寄生电容的目的。

为什么采用Metal材料?

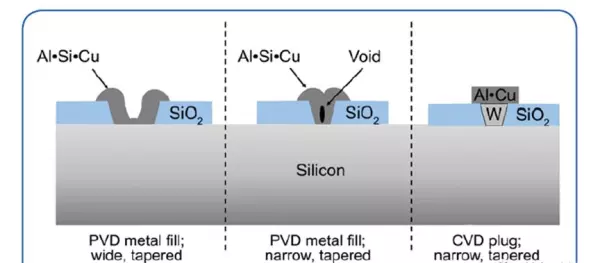

集成电路就是把电路集成起来,类似无数个晶体管组成的组合门电路,在晶体管之间及门电路之间需要使用大量的导线互接,而导线的材料非金属莫属,于是大量的金属材料通过CVD,PVD及其他化学方法构成导线或金属连接部位。

部分High-K材料

部分金属材料

总结性发言

简单总结起来,low-k材料用于层间介质,减小电容,从而减小RC信号延迟,提高器件工作频率。high-k用于提到栅氧化层,提高栅氧厚度,抑制隧穿漏电流,还可用于DRAM存储器,提高存储电荷密度,简化栅介质结构。Metal材料用于晶体管及门电路互连,简单来说就是导线。